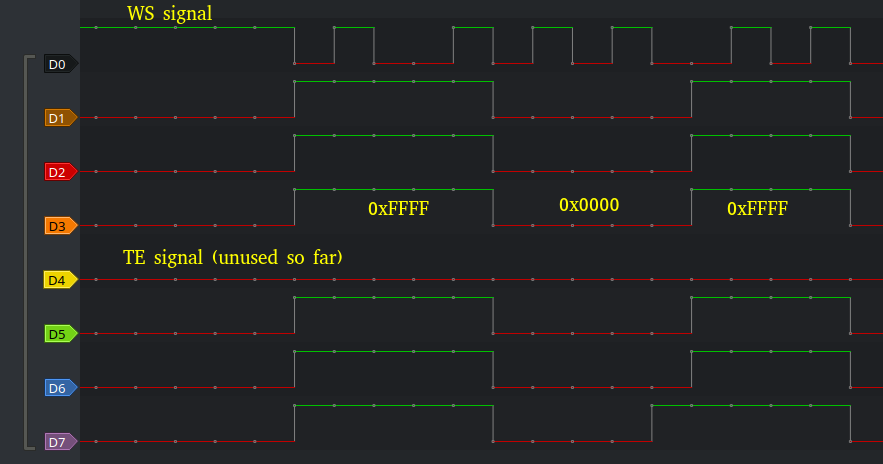

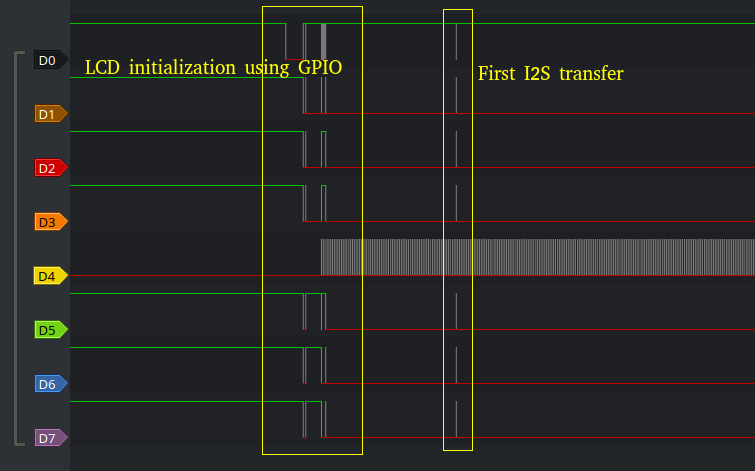

For some weeks now I have trying to interact with a ILI9481-based TFT screen with no much success so far. My intention is to use one of the available I2S peripherals to send the following signal:

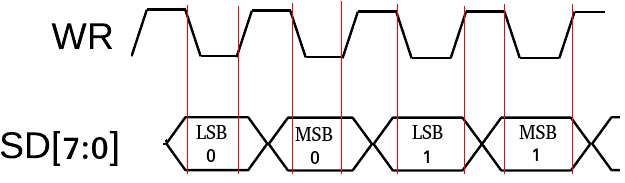

Since the LCD uses 16bpp format, 2 WR clocks per pixel are needed.

I wanted to write my own driver for this, based on the example provided here. This is the approach I took:

1. An external module prepares a 4092-byte buffer (largest word-aligned allowed size given ESP32 DMA limitations) and calls i2s_draw().

2. i2s_draw() sends the buffer over I2S and sets an internal status flag (defined as _Atomic to avoid data races).

3. The external module prepares another buffer of same size while I2S is working.

4. i2s_isr() is executed when the buffer has been sent and it clears the status flag so the external module knows I2S is available again.

5. The external module sends the second buffer over I2S and goes back to step 1 until the whole screen is completely drawn.

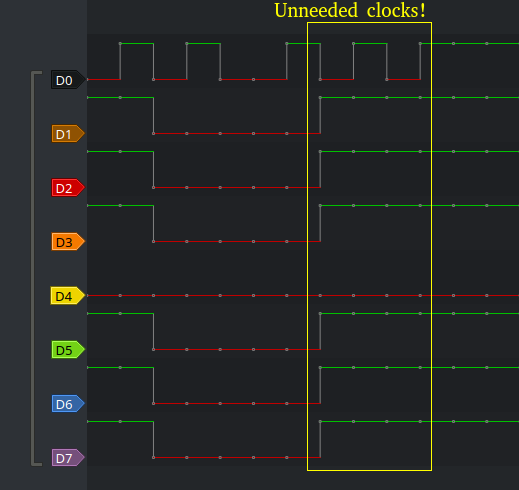

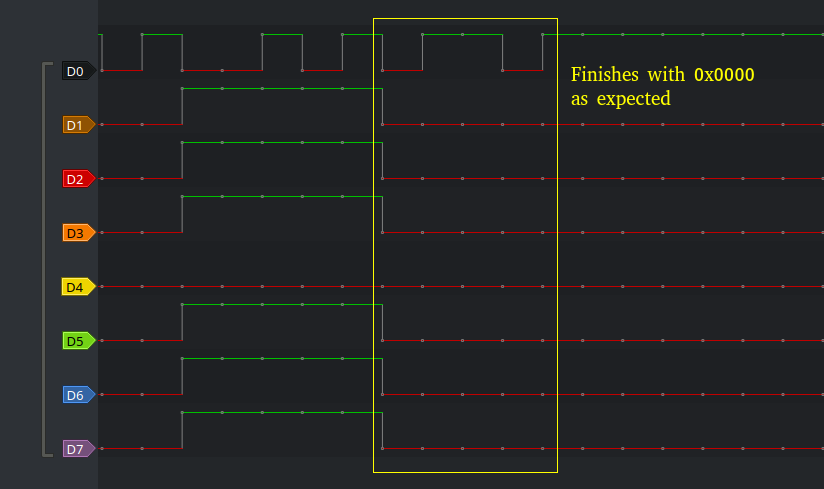

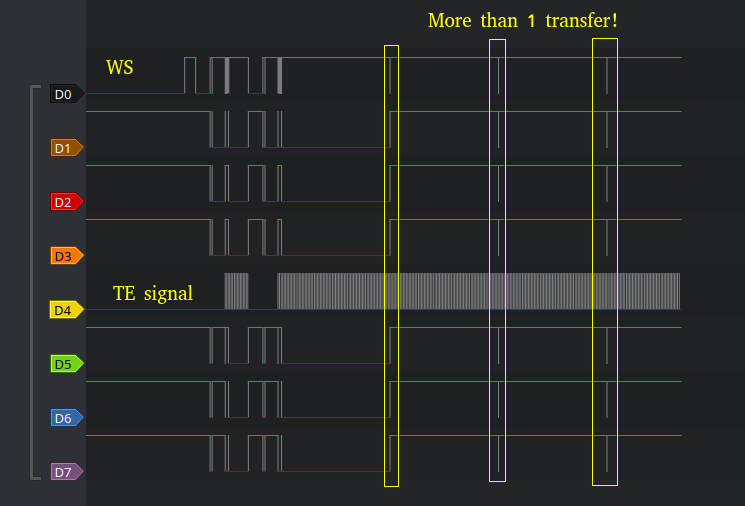

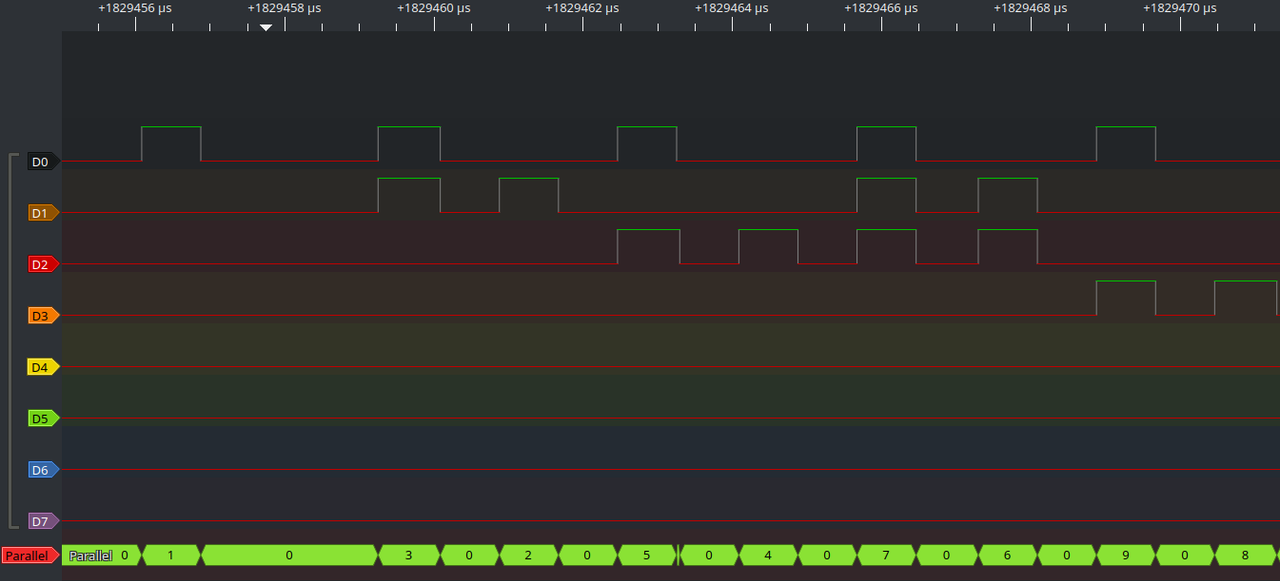

I wanted to keep things simple for the time being, so I avoided dynamic allocation, complex structs (as the ones used by esp-idf component i2s) and FreeRTOS' artifacts as much as possible. The screen does get painted, but not as expected e.g.: I2S would only send the LSB for each pixel and repeat it twice, extra bytes are being sent, polygons look scrambled, etc.

So, I am unsure of how the peripheral should adjusted so as to generate the signal I described above. Considering the buffers are being correctly filled by the external module, what else can I modify from the source code below?

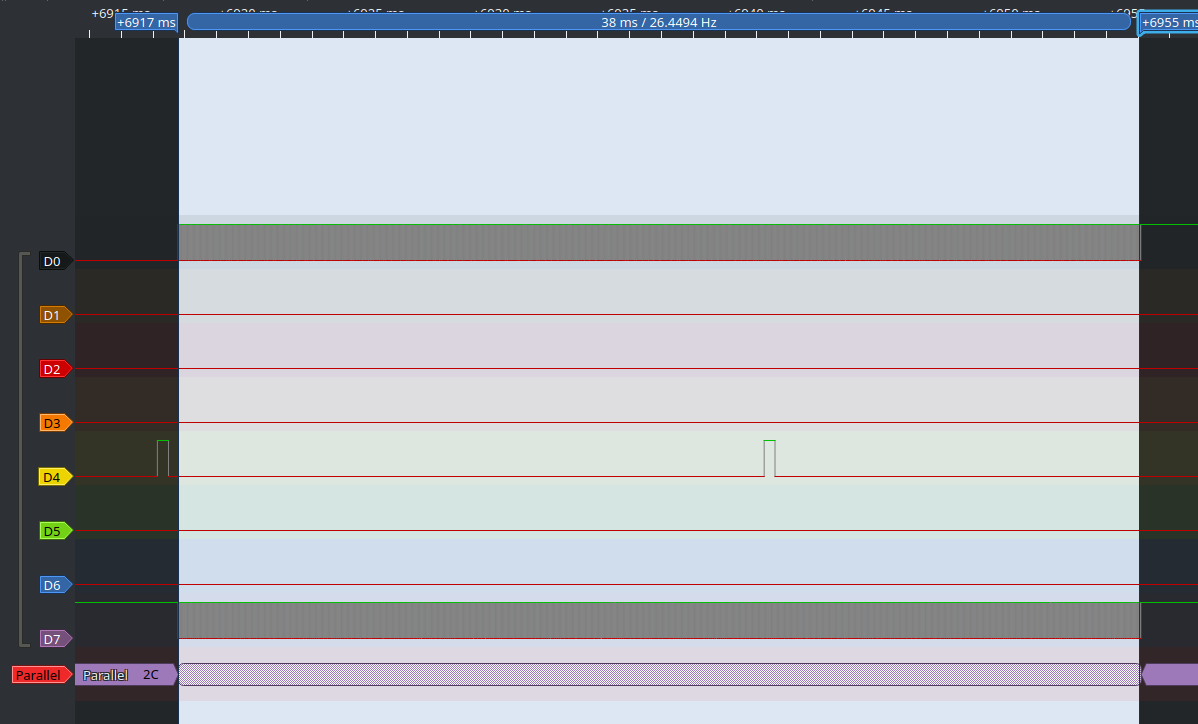

On the other hand, even if clock speed is set to its maximum, tearing effect is still noticeable. I read somewhere I2S should have no problems even with larger displays (considering I am using a 480x320 screen), so is this tearing effect expected? How could I solve it?

Code: Select all

#include "freertos/FreeRTOS.h"

#include "freertos/task.h"

#include "i2sparallel_custom.h"

#include "driver/periph_ctrl.h"

#include "driver/i2s.h"

#include "esp32/rom/lldesc.h"

#include "soc/soc.h"

#include "gfx.h"

#include "esp_log.h"

#include "gpiolcd.h"

#include "global_defs.h"

SemaphoreHandle_t xSemaphore[N_DISPLAY_BUFFERS];

_Atomic volatile bool busy;

static void i2s_setup_peripheral(void);

static void i2s_setup_clock(void);

static void i2s_isr(void *const params);

static void i2s_setup_peripheral(void)

{

enum

{

I2S_TX_FIFO_MODE_16_BIT_DUAL,

I2S_TX_FIFO_MODE_16_BIT_SINGLE,

I2S_TX_CHAN_MODE_MONO

};

/* Enable I2S0 peripheral before modifying any register. */

periph_module_enable(PERIPH_I2S0_MODULE);

/* Set I2S0 in LCD mode. */

I2S0.conf2.lcd_en = 1;

/* Clear TX slave mode so LCD master

* transmission mode is enabled. */

I2S0.conf.tx_slave_mod = 0;

/* Set TX channel mode. */

I2S0.conf_chan.tx_chan_mod = I2S_TX_CHAN_MODE_MONO;

/* Set TX FIFO mode. */

I2S0.fifo_conf.tx_fifo_mod = I2S_TX_FIFO_MODE_16_BIT_DUAL;

/* This bit must always be set, according to TRM. */

I2S0.fifo_conf.tx_fifo_mod_force_en = 1;

I2S0.conf1.tx_pcm_bypass = 1;

I2S0.conf1.tx_stop_en = 1;

I2S0.conf.tx_right_first = 1;

I2S0.conf.tx_msb_right = 1;

/* Define I2S0 transmitter channel bit length. */

I2S0.sample_rate_conf.tx_bits_mod = 32;

/* These bits must always be set, according to TRM

* documentation, when working in LCD mode so LCD

* master transmitting data frame form 2, where 1

* byte is transmitted each time WR is asserted,

* is used. */

I2S0.conf2.lcd_tx_sdx2_en = 1;

I2S0.conf2.lcd_tx_wrx2_en = 1;

}

void i2s_setup_gpio(void)

{

{

uint32_t signal_idx = I2S0O_DATA_OUT8_IDX;

foreach (pin, lcd_pins)

{

/* Route each LCD data pin into I2S0 output signal. */

gpio_matrix_out(*pin, signal_idx++, true, false);

}

}

/* According to TRM, I2S WS signal needs to be inverted. */

gpio_matrix_out(WR, I2S0O_WS_OUT_IDX, true, false);

}

enum

{

OWNER_CPU,

OWNER_DMA

};

LCDWord dma_buffers[N_DISPLAY_BUFFERS][DMA_MAX_SIZE / sizeof (LCDWord)];

static lldesc_t dma_descriptor =

{

.size = DMA_MAX_SIZE,

.length = DMA_MAX_SIZE,

.buf = NULL,

.owner = OWNER_DMA,

.eof = 1

};

static void i2s_setup_dma(void)

{

/* Reset DMA AHB interface. */

I2S0.lc_conf.ahbm_rst = 1;

I2S0.lc_conf.ahbm_rst = 0;

/* Reset in DMA FSM. */

I2S0.lc_conf.in_rst = 1;

I2S0.lc_conf.in_rst = 0;

/* Reset out DMA FSM. */

I2S0.lc_conf.out_rst = 1;

I2S0.lc_conf.out_rst = 0;

/* Set owner bit. */

I2S0.lc_conf.check_owner = 0;

/* Transmit data in burst mode. */

I2S0.lc_conf.out_data_burst_en = 1;

/* Transfer outlink descriptor in burst mode. */

I2S0.lc_conf.outdscr_burst_en = 1;

/* Enable DMA operation over I2S0. */

I2S0.fifo_conf.dscr_en = 1;

/* Set up DMA descriptor address. */

I2S0.out_link.addr = ((uint32_t)(&dma_descriptor)) & I2S_OUTLINK_ADDR;

}

static void i2s_setup_fifo(void)

{

/* Reset DMA AHB interface FIFO buffer. */

I2S0.lc_conf.ahbm_fifo_rst = 1;

I2S0.lc_conf.ahbm_fifo_rst = 0;

/* Reset I2S0 TX channel. */

I2S0.conf.tx_reset = 1;

I2S0.conf.tx_reset = 0;

/* Reset I2S0 TX FIFO buffer. */

I2S0.conf.tx_fifo_reset = 1;

I2S0.conf.tx_fifo_reset = 0;

}

static void i2s_setup_clock(void)

{

/* ***************************************************************

* I2Sn clock frequency is calculated as follows:

*

* fi2s = fPLL / (N + (b/a))

*

* Where:

* fPLL: selected clock frequency. Two options are available:

* PLL_D2_CLK, rated at 160 MHz.

* APLL_CLK (frequency?)

*

* N: CLKM_DIV_NUM

* b: CLKM_DIV_B

* a: CLKM_DIV_A

*

* On the other hand, BCK clock frequency is calculated as follows:

*

* I2SnO_BCK_out = fi2s / M

*

* Where:

*

* M : BCK_DIV_NUM

*

* Note: in this case we are using LCD master transmitting mode.

* ***************************************************************/

/* Set BCK TX clock rate. */

I2S0.sample_rate_conf.tx_bck_div_num = 4;

I2S0.clkm_conf.clkm_div_b = 1;

/* On the original example, it was set to zero. Why? */

I2S0.clkm_conf.clkm_div_a = 0;

/* Set clock frequency denominator. */

I2S0.clkm_conf.clkm_div_num = 1;

/* Activate I2S0 clock. */

I2S0.clkm_conf.clk_en = 1;

/* Enable interrupt trigger when a packet has been sent. */

I2S0.int_ena.out_eof = 1;

I2S0.int_ena.out_total_eof = 1;

/* Enable interrupt trigger when a descriptor error is found. */

I2S0.int_ena.out_dscr_err = 1;

#if 0

/* Why isn't this bit enabled on the example code? */

I2S0.int_ena.out_done = 1;

#endif

}

static void i2s_isr(void *const params)

{

if (I2S0.int_st.out_eof || I2S0.int_st.out_total_eof)

{

I2S0.conf.tx_start = 0;

I2S0.conf.tx_reset = 1;

I2S0.conf.tx_reset = 0;

busy = false;

}

/* Clear interrupt flags. */

I2S0.int_clr.val = I2S0.int_st.val;

}

bool i2s_is_working(void)

{

return busy;

}

static void i2s_setup_isr(void)

{

enum

{

ESP_INTR_FLAGS_NONE

};

intr_handle_t int_handle;

/* Configure interrupt for I2S0. */

const esp_err_t ret = esp_intr_alloc

(

/* Interrupt source */ ETS_I2S0_INTR_SOURCE,

/* Interrupt flags */ ESP_INTR_FLAGS_NONE,

/* Interrupt handler */ i2s_isr,

/* Parameters */ NULL,

/* Return handle */ &int_handle

);

if (ret == ESP_OK)

{

/* This interrupt is not located in IRAM. */

esp_intr_set_in_iram(int_handle, false);

/* Enable interrupt. */

esp_intr_enable(int_handle);

}

else

{

/* Could not initialize I2S0 interrupt handler. */

}

}

void i2s_draw(const LCDWord *const buffer, const size_t elements)

{

busy = true;

dma_descriptor.buf = (uint8_t*)buffer;

dma_descriptor.length = elements * sizeof (*buffer);

if (dma_descriptor.length != DMA_MAX_SIZE)

{

asm volatile ("nop");

}

/* Enable DMA operation over I2S0. */

I2S0.fifo_conf.dscr_en = 1;

/* Start transmission. */

I2S0.out_link.start = 1;

I2S0.conf.tx_start = 1;

}

void i2s_setup(void)

{

/* Setup I2S0 peripheral and its registers. */

i2s_setup_peripheral();

/* Setup GPIO pins used by I2S0. */

i2s_setup_gpio();

/* Setup DMA channel for I2S0. */

i2s_setup_dma();

/* Setup I2S0 clock. */

i2s_setup_clock();

/* Reset I2S0 FIFO buffers. */

i2s_setup_fifo();

/* Setup interrupt handler. */

i2s_setup_isr();

_Static_assert((DMA_MAX_SIZE % sizeof (uint32_t)) == 0, "DMA buffer size is not word-aligned");

_Static_assert(DMA_MAX_SIZE <= 4092, "Exceeded maximum allowed DMA buffer size");

}

Code: Select all

#define lengthof(A) \

_Generic(&(A), \

typeof((A)[0]) *const *: (void)0, \

typeof((A)[0]) **: (void)0, \

default: sizeof(A) / sizeof((A)[0]))

/** This macro simulates a "foreach" instruction (as found in many

* other high-level languages) which loops inside an array of any type.

* Array element mutability is given by the array type itself.

*

* Note: this version requires a C99-compliant compiler and the GCC

* extension "typeof". Compiler flag "-std=gnu99" must be explicitely given. */

#define foreach(element, array) \

for ( \

/* Loop initialization. */ \

\

/* C99 allows defining variables inside a "for" loop,

* but no more than one type can be used at the same time.

* However, this can be easily solved by the use a struct

* which does contain the elements and types we need. */ \

struct \

{ \

/* Pointer to an element in the array.

* By the use of the "typedef" operator,

* pointer type is automatically assigned

* by the compiler. */ \

typeof (*array) *p; \

\

/* As this "foreach" implementation relies on a nested

* "for" loop (which is needed to initialize an integer

* variable out of the pointer above), we need an auxiliary

* variable in order to detect whether the user has inserted

* a "break" instruction inside the inner loop.

*

* If no "break" is entered by the user, this variable

* shall oscillate between 0 and 1 depending on which

* loop is being exited.

*

* Otherwise, this variable will equal zero if the inner

* loop is suddenly exited. This causes the outer loop

* to be exited as well, as it is required that brk == 0. */ \

char brk; \

} __a = \

{ \

.p = array, \

.brk = 0 \

}; \

\

/* Loop condition. */ \

\

/* As explained above, the pointer is used at the same time

* as an iterator by using pointer arithmetic, as substracting

* the address held by the pointer by the address of the array

* first element simply returns the number of elements.

* On the other hand, "brk" must be checked against zero, so

* it can be detected whether the user has used a "break"

* instruction. */ \

(__a.p - array) < lengthof(array) && !__a.brk; \

\

/* Instructions after each iteration. */ \

\

/* When increasing the pointer, the next element from the

* array is pointed. On the other hand, the auxiliary variable

* is decreased so, if no "break" instruction is used by the

* user, it goes back from 1 to 0. */ \

__a.p++, __a.brk-- \

) \

/* This loop is never executed more than once, but it is needed

* to define the target variable the user wants. "__a.brk" is

* incremented for two reasons: to detect a "break" instruction

* entered by the user and to avoid this loop from being

* executed more than once.

* "__a" is hidden to the user and "element" can be used, instead.

* Mutability depends on the array type itself, so "element" cannot

* be modified when using "foreach" on an array of "const" elements. */ \

for (const typeof (*array) *const element = __a.p; !__a.brk; __a.brk++)Xavi