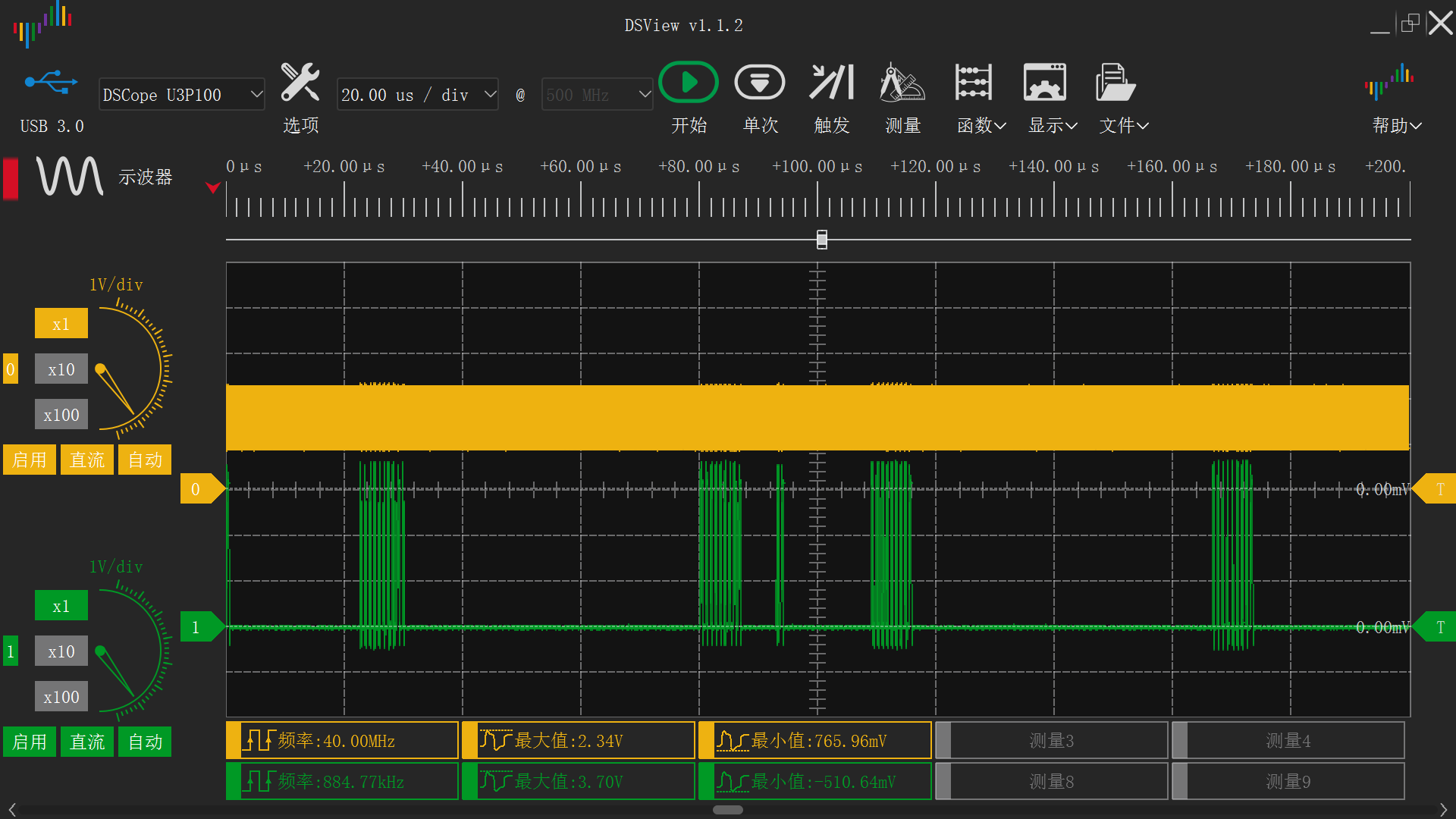

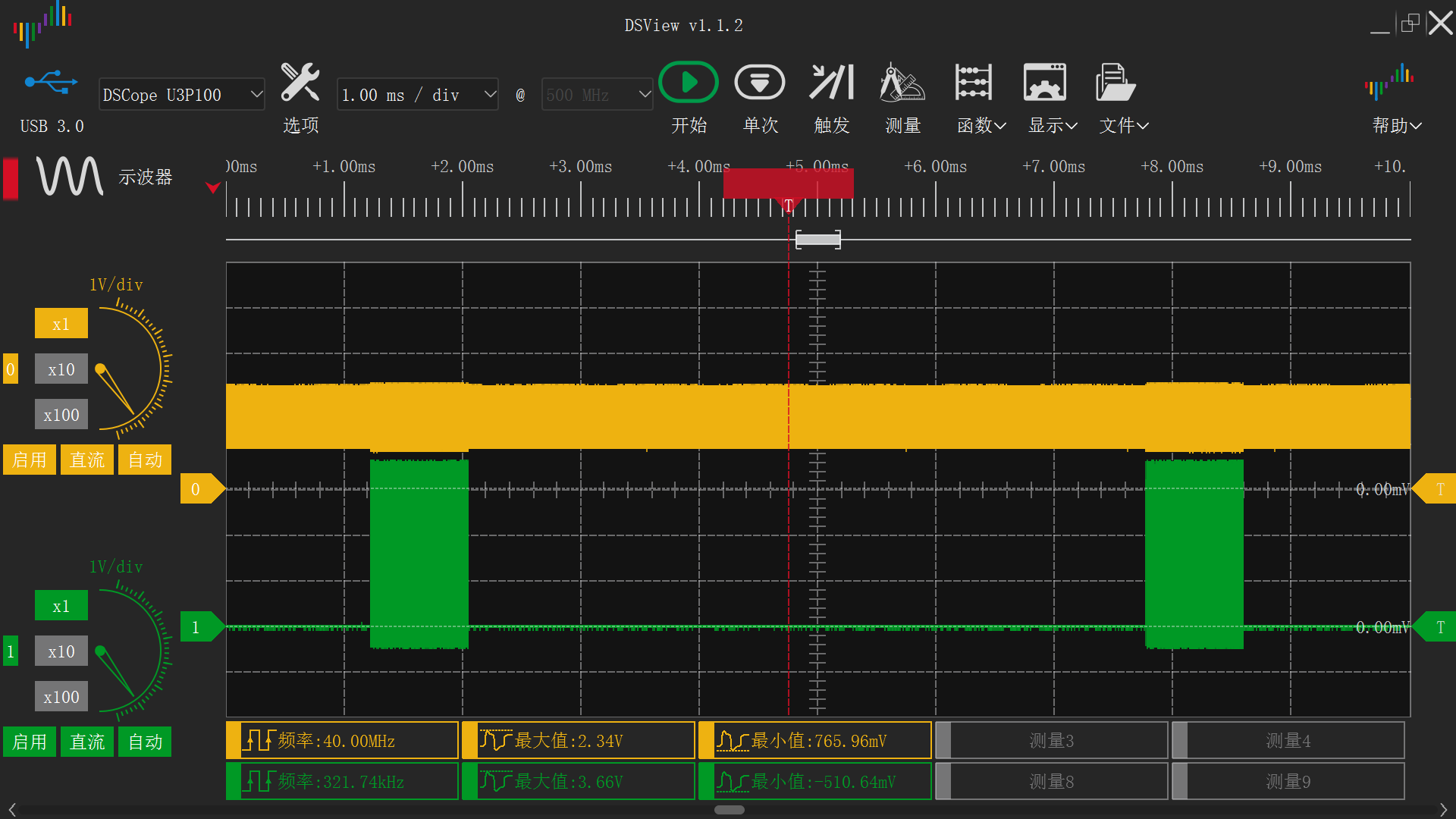

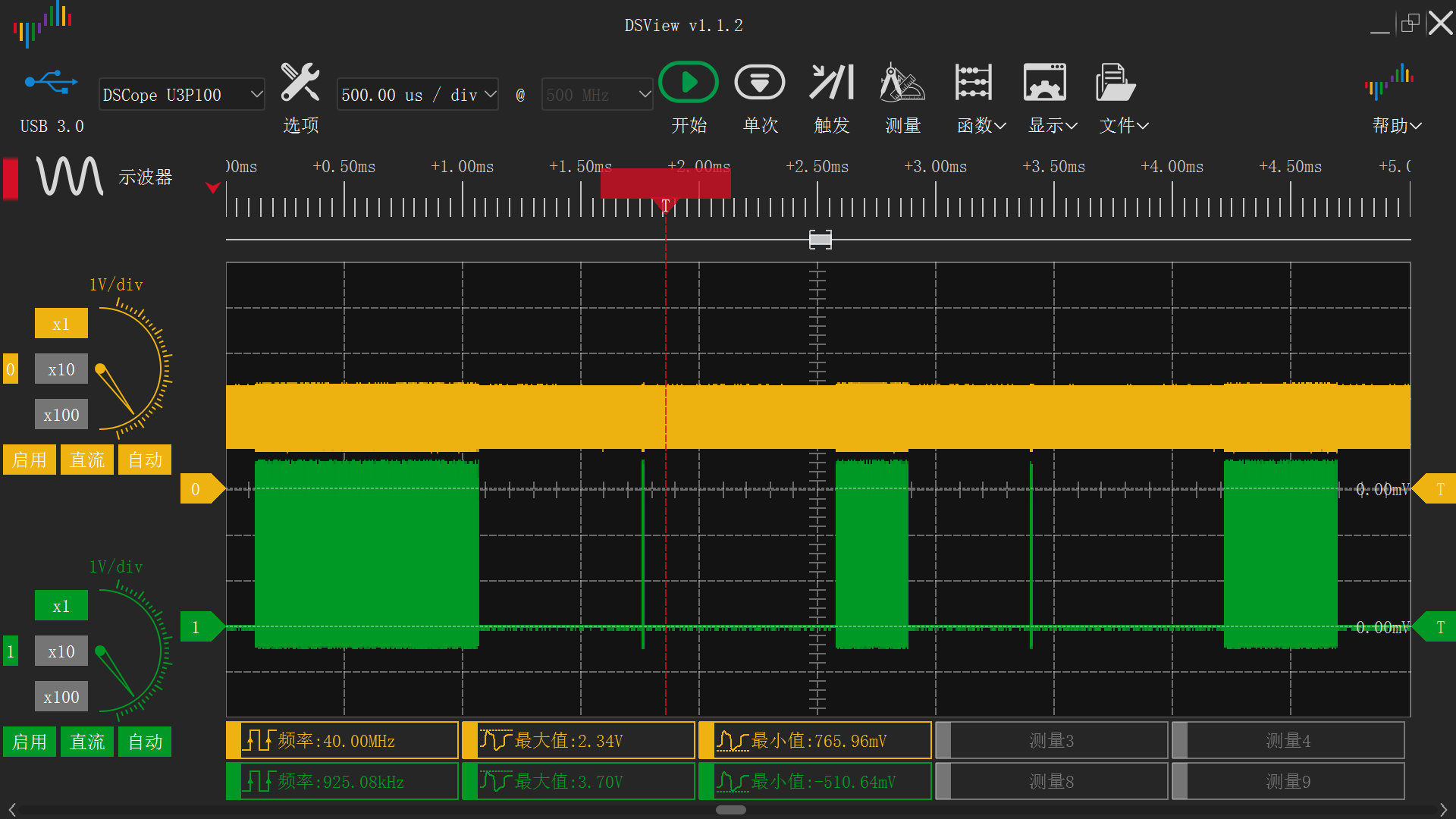

Hi, my oscilloscope has arrived and I managed to get I2S interface running. Well, the good news is, I2S does enable continuous output and the output waveform is suitable for controlling DAC, however, I only managed to get the I2S clock up to 20MHz, which is a bit slower than I've anticipated.ESP_Sprite wrote: ↑Wed Aug 05, 2020 3:02 pmYou may want to set USE_APLL to 1 as well as use a larger dma_buf_len... could be that the issue is that the ISR gets called too often or that the I2S driver has issues generating the frequencies you need.

Are there any method by which I can speed up the I2S clock (BCK) to 40MHz? my current code is like:

Code: Select all

#include "Arduino.h"

#include "driver/i2s.h"

static const i2s_port_t i2s_num = I2S_NUM_0;

static const i2s_config_t i2s_config ={

.mode = (i2s_mode_t)(I2S_MODE_MASTER | I2S_MODE_TX),

.sample_rate = 500000,

.bits_per_sample = I2S_BITS_PER_SAMPLE_16BIT,

.channel_format = I2S_CHANNEL_FMT_RIGHT_LEFT,

.communication_format = (i2s_comm_format_t)(I2S_COMM_FORMAT_I2S_MSB),

.intr_alloc_flags = ESP_INTR_FLAG_LEVEL1,

.dma_buf_count = 8,

.dma_buf_len = 1024,

.use_apll=0,

.tx_desc_auto_clear= true,

.fixed_mclk=40000000

};

static const i2s_pin_config_t pin_config ={

.bck_io_num = 27,

.ws_io_num = 26,

.data_out_num = 25,

.data_in_num = I2S_PIN_NO_CHANGE

};

void setup() {

Serial.begin(115200);

i2s_driver_install(i2s_num, &i2s_config, 0, NULL);

i2s_set_pin(i2s_num, &pin_config);

}

void loop()

{

static uint16_t Value16Bit[18]={65535,0,2,0,3,0,4,0,5,0,6,0,7,0,8,0,9,0};

size_t BytesWritten;

unsigned long tt=micros();

unsigned long count=0;

while (micros()-tt<1000000)

{

i2s_write(i2s_num, Value16Bit, 36, &BytesWritten, portMAX_DELAY);

count+=9;

}

Serial.println(count);

}

Thanks a lot!