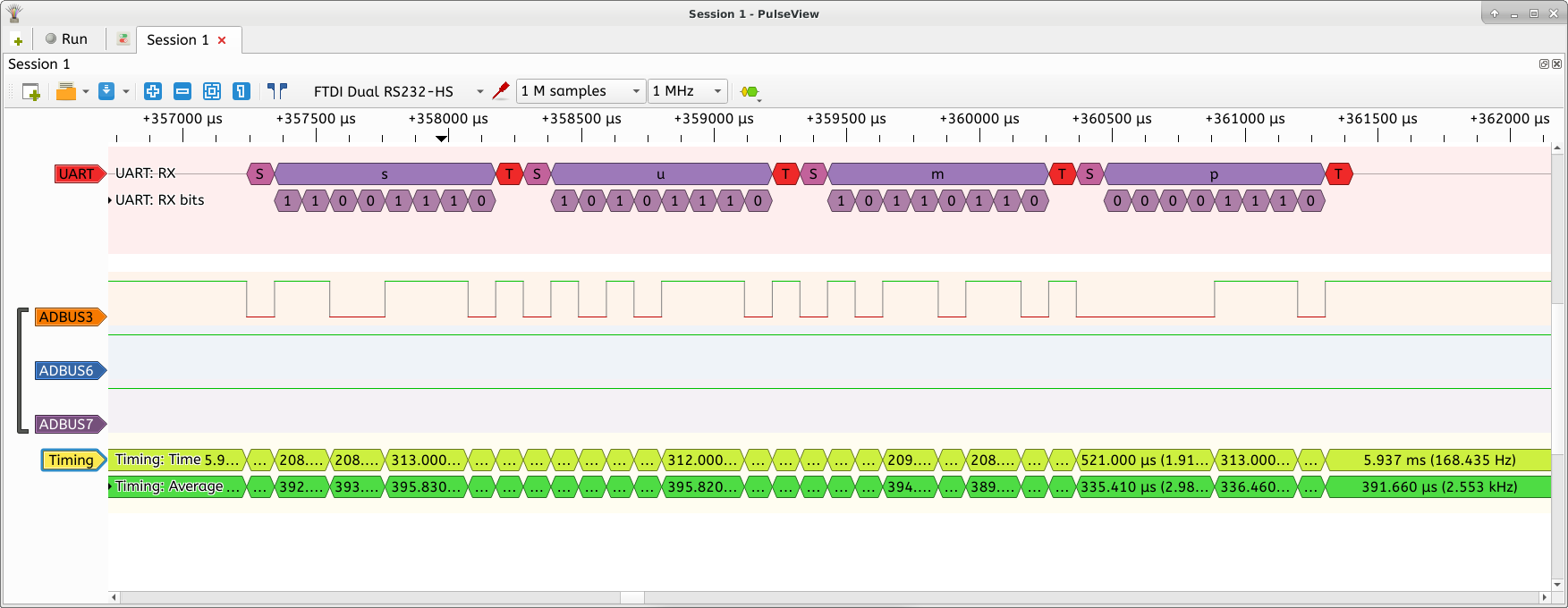

Quite a nice way to get a better understanding of the streams of bits running over the wires of the ESP32.

https://en.wikipedia.org/wiki/Sigrok

Here is the source.

https://github.com/Ebiroll/esp32_sigrok

Does not yet work with Open Bench Logic sniffer but that will be the next step if this project sparks interest.

https://lxtreme.nl/projects/ols/

Another improvement would be using parallel i2s input with DMA to get a higher and smother sampling rate.

Happy holidays