I'm adding the ESP32 to a product I'm developing and had a couple questions:

1) Is there any need to add a 32khz xtal if I don't intend to use the RTC?

2) The technical ref manual says " XTL_CLK is a clock signal generated using an external crystal with a frequency range of 2 ~ 40 MHz" but the hardware design guidelines say "ESP32 can support 40 MHz, 26 MHz, and 24 MHz crystal oscillators". I'm using visualgdb and it has settings for 20, 26, 40, and 80mhz. I was able to program the sparkfun esp32 board (26mhz xtal) with the setting left on 40mhz. I'm confused as how this works. how does visualgdb or the flash download tool set the xtal speed. If I didn't use the download tool, how would I specify it (modify the firmware file or some other means?)

3) I can flash a new firmware on my custom board (currently 20Mhz xtal) but the output of openocd is this

Info : esp32.cpu0: Debug controller was reset (pwrstat=0xE5, after clear 0x00).

Info : esp32.cpu0: Debug controller was reset (pwrstat=0xE5, after clear 0x00).

- would having the wrong xtal freq generate these messages?

Thanks in advance,

Reza

questions/Issues with custom implementation (Xtal, jtag, etc..)

-

rezarethink

- Posts: 20

- Joined: Fri Mar 24, 2017 4:15 am

Re: questions/Issues with custom implementation (Xtal, jtag, etc..)

32k XTAL is optional. If you don't need precise timekeeping during deep sleep, you don't need to add 32k XTAL.

Latest hardware design guidelines (v1.9) say that only 40MHz XTAL is supported. With a 20MHz XTAL, PLL may not be able to lock.

With regards to VisualGDB, i am not sure how exactly it uses the XTAL frequency option. In ESP-IDF XTAL frequency is detected automatically at startup, however it is possible to explicitly set it to 40MHz or 26MHz. So at least 20 and 80 MHz options look odd. I suspect that this is actually not XTAL frequency option but SPI flash frequency. That would match the range of frequencies normally used for interfacing with SPI flash.

"Debug controller was reset (pwrstat=0xE5, after clear 0x00)" does not by itself indicate an error condition. It just says that the processor was reset, and that can happen because of software reset, watchdog reset, external reset, and so on.

If you use 20MHz as XTAL frequency, then JTAG clock frequency has to be no higher than 5MHz (1/4 CPU clock frequency). Also be advised that with unmodified ESP-IDF startup code and a 20MHz XTAL you might not be able to get past PLL enabling stage due to XTAL frequency mismatch. It might get auto-detected as 26MHz though, in which case PLL may lock, and you will get ~61.5MHz APB frequency instead of 80MHz, and proportional error in RTOS ticks / timekeeping.

Latest hardware design guidelines (v1.9) say that only 40MHz XTAL is supported. With a 20MHz XTAL, PLL may not be able to lock.

With regards to VisualGDB, i am not sure how exactly it uses the XTAL frequency option. In ESP-IDF XTAL frequency is detected automatically at startup, however it is possible to explicitly set it to 40MHz or 26MHz. So at least 20 and 80 MHz options look odd. I suspect that this is actually not XTAL frequency option but SPI flash frequency. That would match the range of frequencies normally used for interfacing with SPI flash.

"Debug controller was reset (pwrstat=0xE5, after clear 0x00)" does not by itself indicate an error condition. It just says that the processor was reset, and that can happen because of software reset, watchdog reset, external reset, and so on.

If you use 20MHz as XTAL frequency, then JTAG clock frequency has to be no higher than 5MHz (1/4 CPU clock frequency). Also be advised that with unmodified ESP-IDF startup code and a 20MHz XTAL you might not be able to get past PLL enabling stage due to XTAL frequency mismatch. It might get auto-detected as 26MHz though, in which case PLL may lock, and you will get ~61.5MHz APB frequency instead of 80MHz, and proportional error in RTOS ticks / timekeeping.

-

wormyrocks

- Posts: 2

- Joined: Fri Aug 18, 2017 4:38 pm

Re: questions/Issues with custom implementation (Xtal, jtag, etc..)

Hello,

I am building on top of the WROOM-02 development board and trying to implement precise timekeeping from within deep sleep mode.

I know the WROOM-02 already has an external crystal, but pinouts show that it has external connections for XTAL_P and XTAL_N.

Currently my device time drifts by about 1 minute per hour when asleep, leading me to conclude that it is using the PLL for low power timekeeping.

Will the crystal already in the WROOM-02 work for timekeeping during deep sleep, or does that crystal supply the base clock for the chip?

Finally - besides changing the setting in menuconfig, are there any firmware changes I have to make to support using an external crystal in deep sleep mode?

Thank you!

I am building on top of the WROOM-02 development board and trying to implement precise timekeeping from within deep sleep mode.

I know the WROOM-02 already has an external crystal, but pinouts show that it has external connections for XTAL_P and XTAL_N.

Currently my device time drifts by about 1 minute per hour when asleep, leading me to conclude that it is using the PLL for low power timekeeping.

Will the crystal already in the WROOM-02 work for timekeeping during deep sleep, or does that crystal supply the base clock for the chip?

Finally - besides changing the setting in menuconfig, are there any firmware changes I have to make to support using an external crystal in deep sleep mode?

Thank you!

-

rezarethink

- Posts: 20

- Joined: Fri Mar 24, 2017 4:15 am

Re: questions/Issues with custom implementation (Xtal, jtag, etc..)

Thanks for the feedback. I've since tried it with both a 40Mhz xtal and a 26Mhz xtal. They both seem to start oscillating and I get serial output on the TX line. I've tried it both with this flash module MX25R6435FZNIL0 and I've also desoldered the flash chip from a sparkfun board and tried wiring that in (W25Q32FVSS). I did notice that the pins for the QSPI connection and the SPI connection differ in that pins 3/7 of the flash are reversed. Looks like sparkfun uses the SPI connections. What's the best way to connect flash? This is how sparkfun does it

When I use visualgdb to flash the sparkfun board (following this tutorial: https://visualgdb.com/tutorials/esp32/ ) it works fine and I the application persists in the flash.

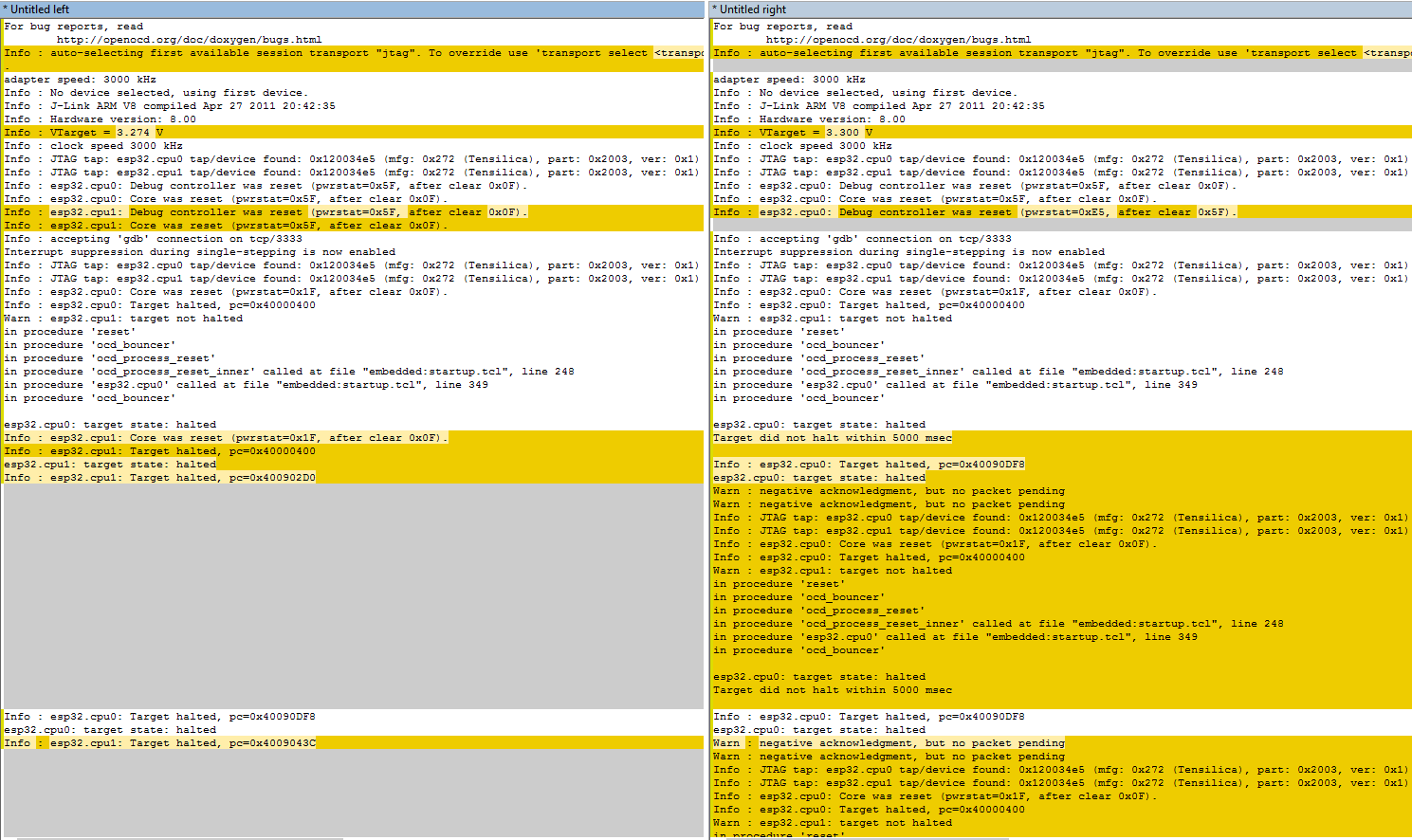

When I try to flash my board which is nearly identical (more closely matches the decoupling of the ref design than the sparkfun board) it doesn't work. The JTAG interface seems to find the chip just fine but is unable to halt/reboot CPU1. Here is a side-by-side comparison of the output from openOCD:

Left works (sparkfun). Right it my board. (link to image: https://goo.gl/zTExkd)

I've gone so far as to remove both the flash chip and the ESP32 chip from the sparkfun board and use them to populate my board but it doesn't help.

Any suggestions would be greatly appreciated!

Thanks in advance,

Reza

When I try to boot up the chip this is the output from the UART from the ESP32ESP32 PIN SIGNAL SPARKFUN FLASH PIN

-------------------------------------------------------------------

31 SPICLK/SD_CLK SCK(6)

32 SPIQ/SD_DATA_0 SO(D1)

33 SPID/SD_DATA_1 SI(D0)

28 SPIHD/SD_DATA_2 #HOLD(D3)

29 SPIWP/SD_DATA_3 #WP(D2)

30 SPICS/SD_CMD #CS

rst:0x10 (RTCWDT_RTC_RESET),boot:0x13 (SPI_FAST_FLASH_BOOT)

flash read err, 1000

Falling back to built-in command interpreter.

OK

>ets Jun 8 2016 00:22:57

rst:0x10 (RTCWDT_RTC_RESET),boot:0x13 (SPI_FAST_FLASH_BOOT)

flash read err, 1000

Falling back to built-in command interpreter.

OK

>ets Jun 8 2016 00:22:57

... REPEATS ---

When I use visualgdb to flash the sparkfun board (following this tutorial: https://visualgdb.com/tutorials/esp32/ ) it works fine and I the application persists in the flash.

When I try to flash my board which is nearly identical (more closely matches the decoupling of the ref design than the sparkfun board) it doesn't work. The JTAG interface seems to find the chip just fine but is unable to halt/reboot CPU1. Here is a side-by-side comparison of the output from openOCD:

Left works (sparkfun). Right it my board. (link to image: https://goo.gl/zTExkd)

I've gone so far as to remove both the flash chip and the ESP32 chip from the sparkfun board and use them to populate my board but it doesn't help.

Any suggestions would be greatly appreciated!

Thanks in advance,

Reza

-

rezarethink

- Posts: 20

- Joined: Fri Mar 24, 2017 4:15 am

Re: questions/Issues with custom implementation (Xtal, jtag, etc..)

One other comment - I tried the ESP serial flash tool with both the Sparkfun board and my board, and it didn't work with either. It seems that the ESP32 drives the RX serial line and I'm unable to send any commands to it (based on the output of my logic analyzer).

-

ESP_Sprite

- Posts: 9764

- Joined: Thu Nov 26, 2015 4:08 am

Re: questions/Issues with custom implementation (Xtal, jtag, etc..)

You are aware that the WROOM-02 contains an ESP8266, not an ESP32? Do you mean the WROOM32?wormyrocks wrote:Hello,

I am building on top of the WROOM-02 development board...

-

ESP_Sprite

- Posts: 9764

- Joined: Thu Nov 26, 2015 4:08 am

Re: questions/Issues with custom implementation (Xtal, jtag, etc..)

rezarethink: No clue why VisualGDB doesn't do the right thing; my guess would be that it expects some kind of firmware to pre-exist in flash that initializes CPU1. Maybe you're better off asking the VisualGDB people this.

On why the serial port does not work: Are you sure you're pulling down GPIO0 and pull up or leave floating GPIO2? That should be the way to enter boot loader mode. If you're using esp-idf, you can then just run 'make flash' to flash the chip.

On why the serial port does not work: Are you sure you're pulling down GPIO0 and pull up or leave floating GPIO2? That should be the way to enter boot loader mode. If you're using esp-idf, you can then just run 'make flash' to flash the chip.

-

rezarethink

- Posts: 20

- Joined: Fri Mar 24, 2017 4:15 am

Re: questions/Issues with custom implementation (Xtal, jtag, etc..)

On the sparkfun I realized that they had an FTDI chip that was driving the RX pin on the ESP32. When I tried using the USB port to communicate, it worked fine.

I then tried it with my board. I was able to get it into the bootloader program by pulling GPIO0 low during boot and read some information from the chip. However, when I try to connect it gets this far..

But the clock is at 6.66Mhz not the 20Mhz SPI speed specified in the ESP download tool (v3.4.9.2).

Any suggestions?

I then tried it with my board. I was able to get it into the bootloader program by pulling GPIO0 low during boot and read some information from the chip. However, when I try to connect it gets this far..

but then it doesn't get past it. I currently have the same flash chip from a sparkfun board connected to the exact same pins on the ESP32. It's communicating...chip sync ok!

ESP32 set baud: 115200

Changing baud rate to 115200

Changed.

mac l: 0xa42a8d00L

mac h: 0x8330ae

crc_cal: 131

crc_read: 131

crc_test: 0

ESP32 mac crc ok

48bit mac

MAC AP : 30AEA42A8D01

MAC STA: 30AEA42A8D00

get mac res: True

('tttest uuuuuuuuuuart : uart reg: ', 220)

(' baudrate: ', 115200)

get crystal: 25344000

SEND ESP SPI ATTACH CMD

But the clock is at 6.66Mhz not the 20Mhz SPI speed specified in the ESP download tool (v3.4.9.2).

Any suggestions?

-

wormyrocks

- Posts: 2

- Joined: Fri Aug 18, 2017 4:38 pm

Re: questions/Issues with custom implementation (Xtal, jtag, etc..)

Ah my mistake. Yes, I mean the WROOM32.ESP_Sprite wrote:You are aware that the WROOM-02 contains an ESP8266, not an ESP32? Do you mean the WROOM32?wormyrocks wrote:Hello,

I am building on top of the WROOM-02 development board...

Who is online

Users browsing this forum: No registered users and 78 guests