Using SPI Master in ESP32-C3

Using SPI Master in ESP32-C3

Hey there, hope everyone is doing well. I started trying the C3 after upgrading ESP-IDF to the latest master state.

And could not refresh one of my epapers using C3 as SPI Master. Maybe someone can give me a hint? Or just show me some sample code?

About DMA channel, I tried to use 1, but the Serial output says:

E (368) spi: spi_bus_initialize(633): invalid dma channel, chip only support spi dma channel auto-alloc

I don't know what value is auto-alloc, but in:

spi_bus_initialize(EPD_HOST, &buscfg, DMA_CHAN);

dma_chan – Either channel 1 or 2, or 0 in the case when no DMA is required. Selecting a DMA channel for a SPI bus allows transfers on the bus to have sizes only limited by the amount of internal memory. Selecting no DMA channel (by passing the value 0) limits the amount of bytes transfered to a maximum of 64

Using 0 I don't get that message and transmits something but I still cannot make it refresh (Same code in ESP32 works ok) and also 0 limits the TX data to 64 bytes.

The class I'm using for SPI is mine: https://github.com/martinberlin/cale-id ... epdspi.cpp

The GPIOs I've used (tried many different combinations so far without luck)

CONFIG_EINK_SPI_MOSI=7

CONFIG_EINK_SPI_CLK=6

CONFIG_EINK_SPI_CS=9

CONFIG_EINK_DC=4

CONFIG_EINK_RST=19

CONFIG_EINK_BUSY=18

I will connect later the Logic analyzer to the PINs and see what is really coming out. But if any of you has an advice or sees something obviously wrong please send me a hint. Thanks in advance

And could not refresh one of my epapers using C3 as SPI Master. Maybe someone can give me a hint? Or just show me some sample code?

About DMA channel, I tried to use 1, but the Serial output says:

E (368) spi: spi_bus_initialize(633): invalid dma channel, chip only support spi dma channel auto-alloc

I don't know what value is auto-alloc, but in:

spi_bus_initialize(EPD_HOST, &buscfg, DMA_CHAN);

dma_chan – Either channel 1 or 2, or 0 in the case when no DMA is required. Selecting a DMA channel for a SPI bus allows transfers on the bus to have sizes only limited by the amount of internal memory. Selecting no DMA channel (by passing the value 0) limits the amount of bytes transfered to a maximum of 64

Using 0 I don't get that message and transmits something but I still cannot make it refresh (Same code in ESP32 works ok) and also 0 limits the TX data to 64 bytes.

The class I'm using for SPI is mine: https://github.com/martinberlin/cale-id ... epdspi.cpp

The GPIOs I've used (tried many different combinations so far without luck)

CONFIG_EINK_SPI_MOSI=7

CONFIG_EINK_SPI_CLK=6

CONFIG_EINK_SPI_CS=9

CONFIG_EINK_DC=4

CONFIG_EINK_RST=19

CONFIG_EINK_BUSY=18

I will connect later the Logic analyzer to the PINs and see what is really coming out. But if any of you has an advice or sees something obviously wrong please send me a hint. Thanks in advance

epdiy collaborator | http://fasani.de Fan of Espressif MCUs and electronic design

Re: Using SPI Master in ESP32-C3

Forgot to mention, dev board is this one:

https://docs.espressif.com/projects/esp ... -documents

being a C3 it should be SPI master capable right? I’m hitting this blocker that it does simply not let me set the DMA channel to 1: E (368) spi: spi_bus_initialize(633): invalid dma channel, chip only support spi dma channel auto-alloc

It does that also in the latest IDF version, example for SPI master

https://docs.espressif.com/projects/esp ... -documents

being a C3 it should be SPI master capable right? I’m hitting this blocker that it does simply not let me set the DMA channel to 1: E (368) spi: spi_bus_initialize(633): invalid dma channel, chip only support spi dma channel auto-alloc

It does that also in the latest IDF version, example for SPI master

epdiy collaborator | http://fasani.de Fan of Espressif MCUs and electronic design

-

ESP-Marius

- Posts: 74

- Joined: Wed Oct 23, 2019 1:49 am

Re: Using SPI Master in ESP32-C3

For C3 on latest master the dma_chan value should be either SPI_DMA_DISABLED or SPI_DMA_CH_AUTO (it uses the general DMA peripheral so there is no dedicated SPI channels anymore)

There's an internal MR in review to update the examples to better reflect this. Sorry if they confused you!

There's an internal MR in review to update the examples to better reflect this. Sorry if they confused you!

Re: Using SPI Master in ESP32-C3

Thanks Marius,

did that and compiled. It sets then DMA_CHANNEL to 0, it should be a bit more descriptive, because right now how is described in the function vs error:

spi_bus_initialize(host, bus_config, int dma_chan): Selecting no DMA channel (by passing the value 0) limits the amount of bytes transfered to a maximum of 64

Error: invalid dma channel, chip only support spi dma channel auto-alloc

You don't get that 0 is the auto-alloc. If I get it right doing this also limits the TX data size to 64 bytes.

Sadly even doing this, connecting the logic analyzer I don't see SPI data coming out of MOSI, only some strange noise. Will check, compile the SPI Master lcd example and try again.

UPDATE: After trying to update the define DMA_CHAN to 0

I built again the ESP-IDF SPI Master example lcd and I get the following

I (331) cpu_start: Starting scheduler.

LCD ID: 00000000

ILI9341 detected.

LCD ILI9341 initialization.

E (820) spi_master: check_trans_valid(694): txdata transfer > host maximum

assertion "ret==ESP_OK" failed: file "../main/spi_master_example_main.c", line 360, function: send_line

Clearly hitting the 64 bytes TX data maximum so that part should be also updated in that MR

did that and compiled. It sets then DMA_CHANNEL to 0, it should be a bit more descriptive, because right now how is described in the function vs error:

spi_bus_initialize(host, bus_config, int dma_chan): Selecting no DMA channel (by passing the value 0) limits the amount of bytes transfered to a maximum of 64

Error: invalid dma channel, chip only support spi dma channel auto-alloc

You don't get that 0 is the auto-alloc. If I get it right doing this also limits the TX data size to 64 bytes.

Sadly even doing this, connecting the logic analyzer I don't see SPI data coming out of MOSI, only some strange noise. Will check, compile the SPI Master lcd example and try again.

UPDATE: After trying to update the define DMA_CHAN to 0

I built again the ESP-IDF SPI Master example lcd and I get the following

I (331) cpu_start: Starting scheduler.

LCD ID: 00000000

ILI9341 detected.

LCD ILI9341 initialization.

E (820) spi_master: check_trans_valid(694): txdata transfer > host maximum

assertion "ret==ESP_OK" failed: file "../main/spi_master_example_main.c", line 360, function: send_line

Clearly hitting the 64 bytes TX data maximum so that part should be also updated in that MR

epdiy collaborator | http://fasani.de Fan of Espressif MCUs and electronic design

Re: Using SPI Master in ESP32-C3

Here is what I get comparing ESP32-wrover with C3 (imgur link)

https://i.imgur.com/mkzKnux.png

ESP32-Wrover

(Sorry forgot to connect Clock)

(Sorry forgot to connect Clock)

ESP32-C3

Same Firmware, just changing set-target esp32c3. For me is really strange since Clock is not clock, and Mosi is not mosi, the only thing that looks similar is Chip select that is down while transmitting. Has this been tested successfully with the LCD display?

https://i.imgur.com/mkzKnux.png

ESP32-Wrover

(Sorry forgot to connect Clock)

(Sorry forgot to connect Clock)ESP32-C3

Same Firmware, just changing set-target esp32c3. For me is really strange since Clock is not clock, and Mosi is not mosi, the only thing that looks similar is Chip select that is down while transmitting. Has this been tested successfully with the LCD display?

epdiy collaborator | http://fasani.de Fan of Espressif MCUs and electronic design

-

ESP-Marius

- Posts: 74

- Joined: Wed Oct 23, 2019 1:49 am

Re: Using SPI Master in ESP32-C3

Are you sure you connected everything according to the C3 pinouts? And sampled at a reasonable sampling frequency? (I see it's selected as 100 KHz in your picture)

I took a quick look and my C3 signals looked OK, but I was unable properly print anything to the display though. We'll look at it and make sure the example is able to be used with C3.

I took a quick look and my C3 signals looked OK, but I was unable properly print anything to the display though. We'll look at it and make sure the example is able to be used with C3.

Re: Using SPI Master in ESP32-C3

In this I used only 50 Khz setting in SPI (Same settings in the ESP32 that you can see above)

But I agree it's not a nice capture, will do it again this weekend, thanks for taking a look it will be a great help to get SPI running in ESP-IDF.

Please send me a signal if the LCD SPI Master example compiles and I will try that first connecting the logic analyzer. I think the PINS are ok I took most of them from that example.

But I agree it's not a nice capture, will do it again this weekend, thanks for taking a look it will be a great help to get SPI running in ESP-IDF.

Please send me a signal if the LCD SPI Master example compiles and I will try that first connecting the logic analyzer. I think the PINS are ok I took most of them from that example.

epdiy collaborator | http://fasani.de Fan of Espressif MCUs and electronic design

Re: Using SPI Master in ESP32-C3

Dear ESP-Marius,

upgrading to the latest master version of ESP-IDF:

martin@martin-IdeaPad:~/esp/esp-idf$ git pull

From https://github.com/espressif/esp-idf

1cb31e509..cf457d412 master -> origin/master

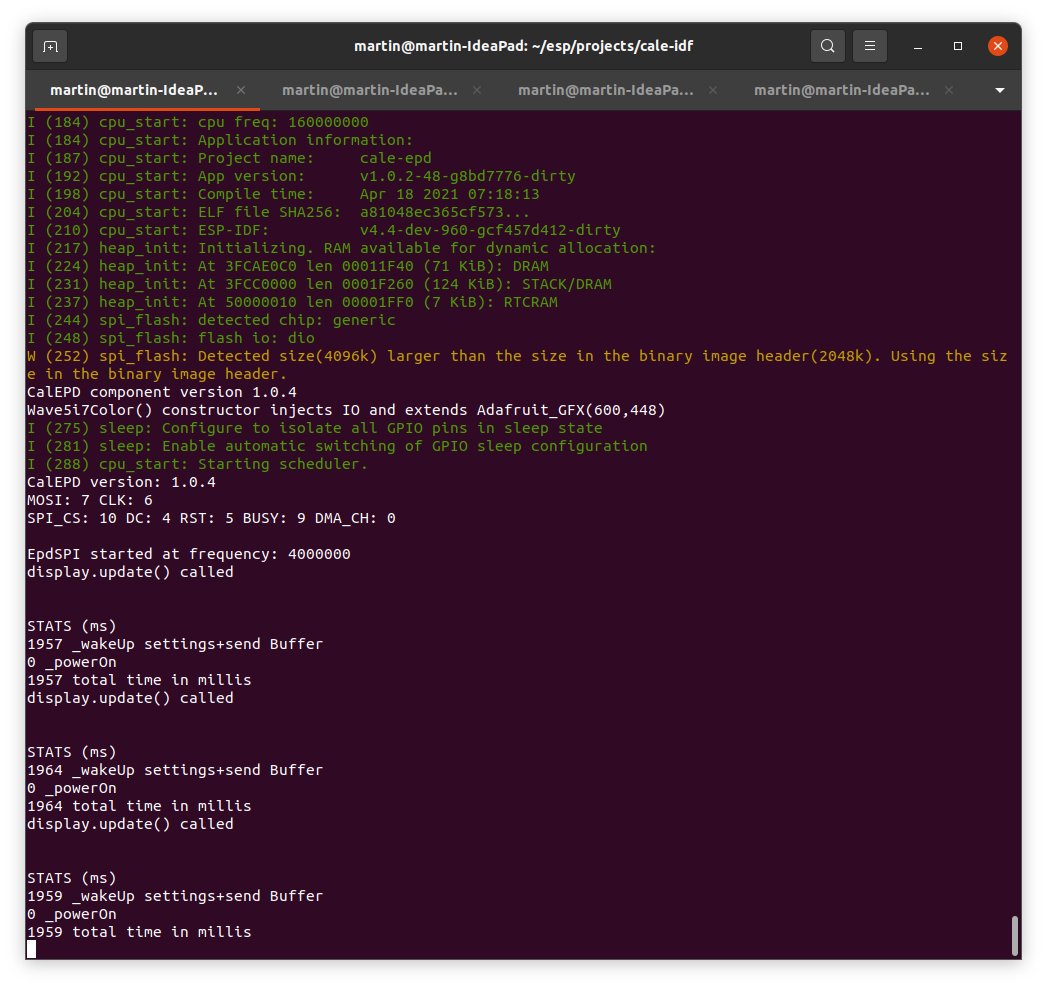

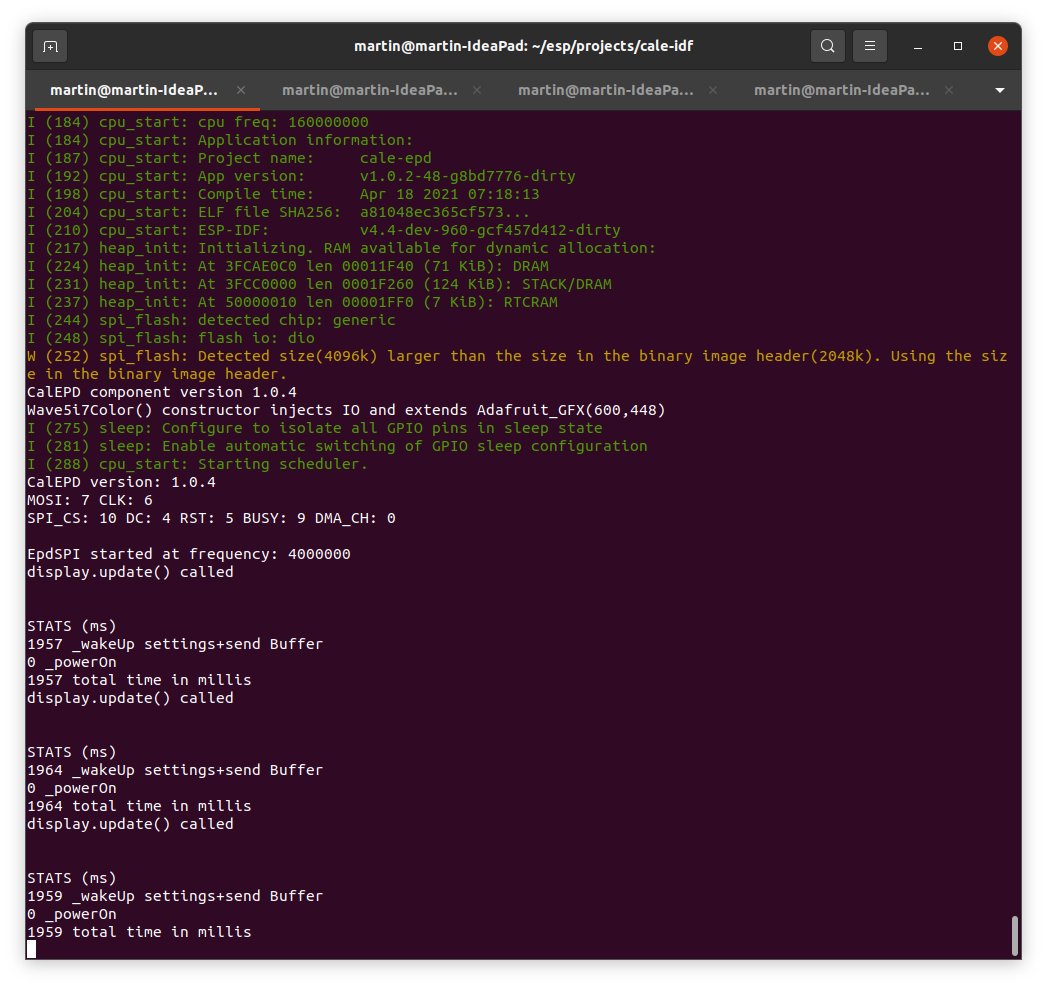

I'm getting this in the Serial output of the C3:

ESP-ROM:esp32c3-20200918

Build:Sep 18 2020

rst:0x3 (RTC_SW_SYS_RST),boot:0xc (SPI_FAST_FLASH_BOOT)

Saved PC:0x403d11b2

SPIWP:0xee

mode:DIO, clock div:1

load:0x3fcd6100,len:0x1630

load:0x403ce000,len:0x880

load:0x403d0000,len:0x2ba4

entry 0x403ce000

I (34) boot: ESP-IDF v4.4-dev-960-gcf457d412-dirty 2nd stage bootloader

I (35) boot: compile time 22:21:15

I (35) boot: chip revision: 2

E (38) boot_comm: can't run on lower chip revision, expected 2, found 3

Serial message looks misleading, since if my chip revision is 2, should be:

can't run on lower chip revision, expected 3, found 2

(It seems mine is 2 or at least that says the serial output)

upgrading to the latest master version of ESP-IDF:

martin@martin-IdeaPad:~/esp/esp-idf$ git pull

From https://github.com/espressif/esp-idf

1cb31e509..cf457d412 master -> origin/master

I'm getting this in the Serial output of the C3:

ESP-ROM:esp32c3-20200918

Build:Sep 18 2020

rst:0x3 (RTC_SW_SYS_RST),boot:0xc (SPI_FAST_FLASH_BOOT)

Saved PC:0x403d11b2

SPIWP:0xee

mode:DIO, clock div:1

load:0x3fcd6100,len:0x1630

load:0x403ce000,len:0x880

load:0x403d0000,len:0x2ba4

entry 0x403ce000

I (34) boot: ESP-IDF v4.4-dev-960-gcf457d412-dirty 2nd stage bootloader

I (35) boot: compile time 22:21:15

I (35) boot: chip revision: 2

E (38) boot_comm: can't run on lower chip revision, expected 2, found 3

Serial message looks misleading, since if my chip revision is 2, should be:

can't run on lower chip revision, expected 3, found 2

(It seems mine is 2 or at least that says the serial output)

epdiy collaborator | http://fasani.de Fan of Espressif MCUs and electronic design

Re: Using SPI Master in ESP32-C3

Hello ESP-Marius,

Someone hinted me that is possible to skip that error updating the sdkconfig:

# CONFIG_ESP32C3_REV_MIN_3 is not set

CONFIG_ESP32C3_REV_MIN_2=y

CONFIG_ESP32C3_REV_MIN=2

Now it runs without that error but still cannot update the epaper using ESP32C3 as SPI Master.

Can you please confirm me if the ESP32C3 revision 2 can work as SPI Master?

I'm using this GPIOs (With same config and standard SPI pins on esp32 it works perfectly)

Someone hinted me that is possible to skip that error updating the sdkconfig:

# CONFIG_ESP32C3_REV_MIN_3 is not set

CONFIG_ESP32C3_REV_MIN_2=y

CONFIG_ESP32C3_REV_MIN=2

Now it runs without that error but still cannot update the epaper using ESP32C3 as SPI Master.

Can you please confirm me if the ESP32C3 revision 2 can work as SPI Master?

I'm using this GPIOs (With same config and standard SPI pins on esp32 it works perfectly)

epdiy collaborator | http://fasani.de Fan of Espressif MCUs and electronic design

-

PasserbyAAA

- Posts: 2

- Joined: Mon Apr 19, 2021 4:34 am

Re: Using SPI Master in ESP32-C3

Hi fasani,

On ESP32C3, for the SPI DMA channel setting:

You should either set the `dma_chan` to SPI_DMA_DISABLED or SPI_DMA_CH_AUTO, both of these are enums in spi_common.h. The former one is to use the SPI without DMA, the transaction length is limitted to 64B. The latter one will make the driver to allocate a DMA channel. But the SPI transaction length is still limitted by the SPI peripheral, where the max length per transaction would be 262143 bits.

Besides, we tested both ESP32C3 ECO2 and ECO3 with the latest esp-idf commit on github and they work. https://github.com/espressif/esp-idf/co ... 2ee86199af

What if you disconnect the LCD, and connect the default SPI CS (IO10), CLK(IO6) and MOSI(IO7) pins to the logic analyser to see the output there?

On ESP32C3, for the SPI DMA channel setting:

Code: Select all

esp_err_t spi_bus_initialize(spi_host_device_t host_id, const spi_bus_config_t *bus_config, spi_dma_chan_t dma_chan);Besides, we tested both ESP32C3 ECO2 and ECO3 with the latest esp-idf commit on github and they work. https://github.com/espressif/esp-idf/co ... 2ee86199af

What if you disconnect the LCD, and connect the default SPI CS (IO10), CLK(IO6) and MOSI(IO7) pins to the logic analyser to see the output there?

Who is online

Users browsing this forum: No registered users and 358 guests