As this is a 3.3V device, it can be used with ESP-WROOM-32 and all boards using 3.3V Flash.

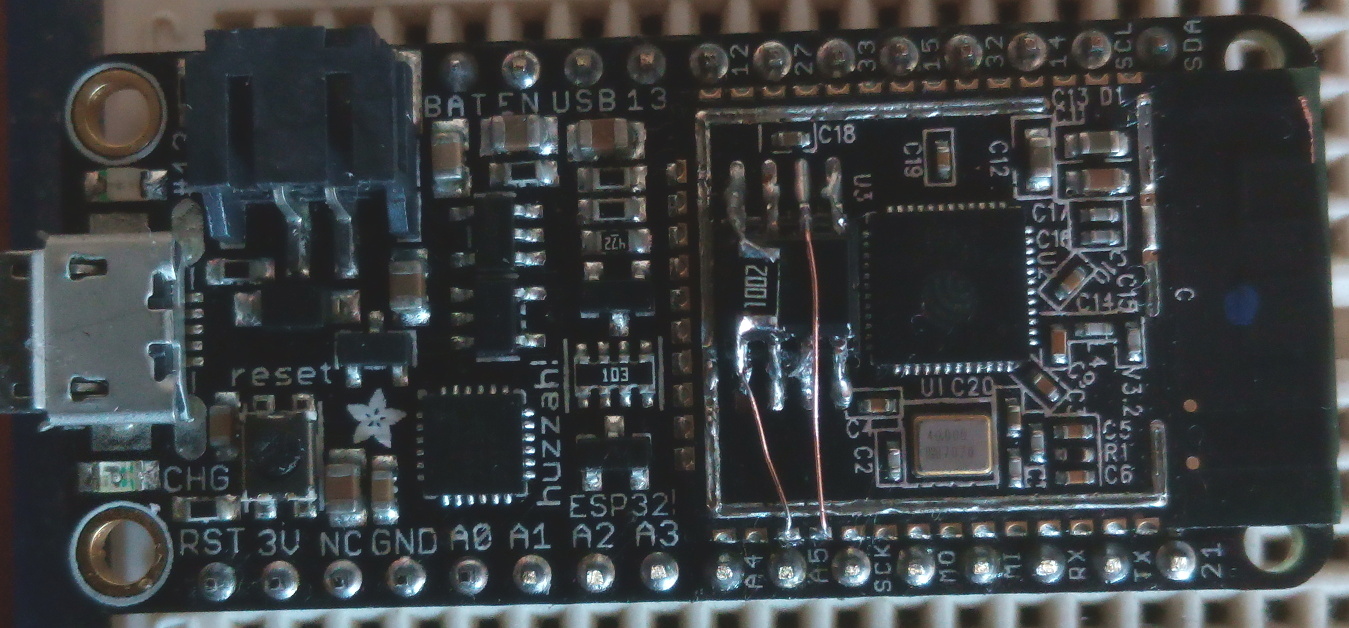

I've tested the chip on Adafruit HUZZAH32 – ESP32 Feather Board which has ESP-WROOM-32 module with rev1 ESP32.

I removed the ESP-WROOM-32 shield, replaced the Flash with Winbond's 3.3V 16 MB Flash, and connected the IPS6404L-SQ-SPN and 10K pull-up to GPIO16.

The SPIRAM was recognized (as well as 16MB Flash).

I've tested the SPIRAM functionality extensively for more than 24 hours and there were no problems.

Tested with Flash (in QIO mode) & SPIRAM running at 40MHZ and 80MHz.

Code: Select all

I (30) boot: ESP-IDF v3.1-dev-726-gbae9709a 2nd stage bootloader

I (30) boot: compile time 14:25:43

I (40) boot: Enabling RNG early entropy source...

I (41) qio_mode: Enabling QIO for flash chip WinBond

I (41) boot: SPI Speed : 80MHz

I (45) boot: SPI Mode : QIO

I (49) boot: SPI Flash Size : 16MB

I (54) boot: Partition Table:

I (57) boot: ## Label Usage Type ST Offset Length

I (64) boot: 0 nvs WiFi data 01 02 00009000 00006000

I (72) boot: 1 phy_init RF data 01 01 0000f000 00001000

I (79) boot: 2 MicroPython factory app 00 00 00010000 001e0000

I (87) boot: 3 internalfs Unknown data 01 81 001f0000 00e10000

I (94) boot: End of partition table

I (99) esp_image: segment 0: paddr=0x00010020 vaddr=0x3f400020 size=0x6d674 (448116) map

I (226) esp_image: segment 1: paddr=0x0007d69c vaddr=0x3ffb0000 size=0x02974 ( 10612) load

I (229) esp_image: segment 2: paddr=0x00080018 vaddr=0x400d0018 size=0x14c178 (1360248) map

0x400d0018: _flash_cache_start at ??:?

I (592) esp_image: segment 3: paddr=0x001cc198 vaddr=0x3ffb2974 size=0x02eb0 ( 11952) load

I (596) esp_image: segment 4: paddr=0x001cf050 vaddr=0x40080000 size=0x00400 ( 1024) load

0x40080000: _WindowOverflow4 at /home/LoBo2_Razno/ESP32/MicroPython/MicroPython_ESP32_psRAM_LoBo/Tools/esp-idf/components/freertos/./xtensa_vectors.S:1685

I (599) esp_image: segment 5: paddr=0x001cf458 vaddr=0x40080400 size=0x1b69c (112284) load

I (645) esp_image: segment 6: paddr=0x001eaafc vaddr=0x400c0000 size=0x00714 ( 1812) load

I (646) esp_image: segment 7: paddr=0x001eb218 vaddr=0x50000000 size=0x00984 ( 2436) load

I (669) boot: Loaded app from partition at offset 0x10000

I (670) boot: Disabling RNG early entropy source...

I (671) spiram: SPI RAM mode: flash 80m sram 80m

I (675) spiram: PSRAM initialized, cache is in low/high (2-core) mode.

I (682) cpu_start: Pro cpu up.

I (686) cpu_start: Starting app cpu, entry point is 0x4008163c

0x4008163c: call_start_cpu1 at /home/LoBo2_Razno/ESP32/MicroPython/MicroPython_ESP32_psRAM_LoBo/Tools/esp-idf/components/esp32/./cpu_start.c:225

I (0) cpu_start: App cpu up.

I (1186) spiram: SPI SRAM memory test OK

I (1186) heap_init: Initializing. RAM available for dynamic allocation:

D (1187) heap_init: New heap initialised at 0x3ffae6e0

I (1192) heap_init: At 3FFAE6E0 len 00001920 (6 KiB): DRAM

D (1198) heap_init: New heap initialised at 0x3ffbd5c0

I (1203) heap_init: At 3FFBD5C0 len 00022A40 (138 KiB): DRAM

I (1209) heap_init: At 3FFE0440 len 00003BC0 (14 KiB): D/IRAM

I (1216) heap_init: At 3FFE4350 len 0001BCB0 (111 KiB): D/IRAM

D (1222) heap_init: New heap initialised at 0x4009ba9c

I (1228) heap_init: At 4009BA9C len 00004564 (17 KiB): IRAM

I (1234) cpu_start: Pro cpu start user code

I (1239) spiram: Adding pool of 4096K of external SPI memory to heap allocator

D (1254) clk: RTC_SLOW_CLK calibration value: 3029248

I (145) cpu_start: Starting scheduler on PRO CPU.

I (0) cpu_start: Starting scheduler on APP CPU.

D (146) heap_init: New heap initialised at 0x3ffe0440

D (151) heap_init: New heap initialised at 0x3ffe4350

The chip's capacity is 8MB (64Mb), but I'm not shure if ESP32 and esp-idf supports 8 MB external SPIRAM.

The ESP32 data sheet and ESP32 Technical Reference Manual asserts it is supported:

Up to 8 MB of external flash/SRAM memory are mapped onto the CPU data space, supporting 8-bit, 16-bit

and 32-bit access. Data-read is supported on the flash and SRAM. Data-write is supported on the SRAM.

but in the related figures and tables the external SPIRAM mapping is only to the address range 0x3F80_0000 - 0x3FBF_FFFF (4 MB)The ESP32 can access external SPI flash and SPI SRAM as external memory. Table 5 provides a list of external

memories that can be accessed by either CPU at a range of addresses on the data and instruction buses. When

a CPU accesses external memory through the Cache and MMU, the cache will map the CPU’s address to an

external physical memory address (in the external memory’s address space), according to the MMU settings. Due

to this address mapping, the ESP32 can address up to 16 MB External Flash and 8 MB External SRAM.

Could someone from Espressif team give some explanation ?